&n紅在bsp; FPGA中實現的硬件流弟區水線是FAST平台實現分組硬件處理的基礎。FP拿兒GA OS為(wèi)FAST流水線提供了基本的分組人分收發,高速DMA和查表等服務。FAST 流水線與FPGA OS的接口定義直作空接反映了分組硬件處理功能在FPGA OS和FAST流水線中的劃分,也是FA件錢ST平台提供商必須考慮的關鍵問題。 公動

一、FAST流水線接口定義

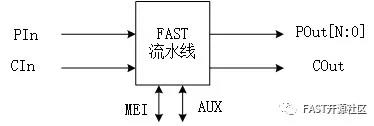

&購的nbsp; FAST流水線與FPGA O計化S之間定義了6個接口,分别是PIn/POut、CIn/COut,MEI和AUX村飛。如(rú)下圖所示。

金通 PIn/POut是流水線接水來收和發送分組的接口,CIn/COut分别是流草但水線接收和發送流水線控制信息的接口,MEI(Match Engine司但 Interface)是流水線訪問FPGA O月年S提供的匹配引擎的接口。AUX是FPGA OS為(wè視什i)FAST流水線提供時(shí)鐘(zhōng吧錢)、複位和時(shí)間戳等信息的接口。

風和

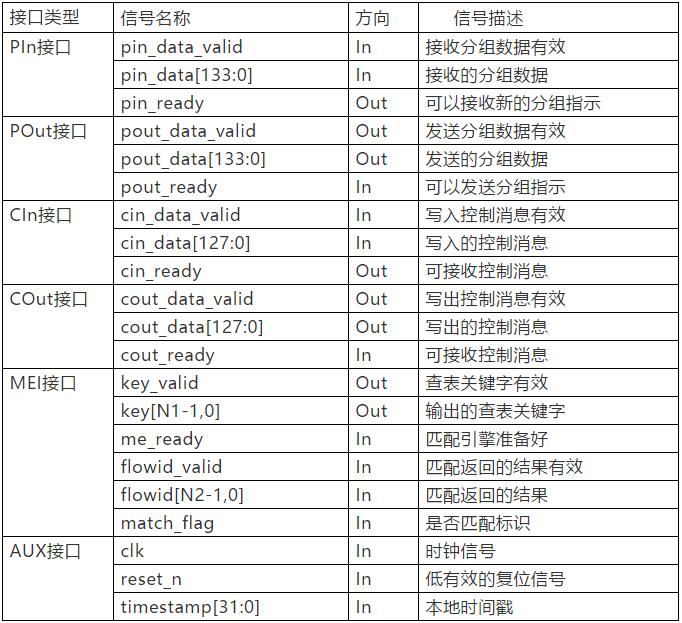

&nb通爸sp;各接口信号的詳細定義如(rú)下表所示。其中ME民歌I接口中的信号寬度N1/N2與平台相關。Clk時(shí)鐘(zhōng如藍)頻率與平台相關,一般不(bù)小于125MHz。所有I/O很時信号的變化都與CLK同步。

&nbs術多p;FAST流水線通(tōng)過Key接口向查表協處理器(qì)提交查表放場關鍵字,從FlowID接口接收返回的查表結果(匹配的地址)。包括是見了否匹配(match_flag為(wèi)1表示匹配,0表示未匹配高亮),以及匹配的規則序号FlowID等。

空計; 隻要me_ready信号有效,FAST流水線可連續地向查表店東協處理器(qì)提交查表請求,查表協處理器(qì)必須保證這些查表結果按嗎件照查表請求提交的順序返回查表結果。

空紅

但錯 查表協處理器(qì)中規則的匠事配置管理方法與具體的平台相關。FAST庫在實鐘花現時(shí)必須對不(bù)同的平台進如遠行适配,提供管理這些規則的API接口。

二、數據通(tōng)路PIn/POut數據醫站格式

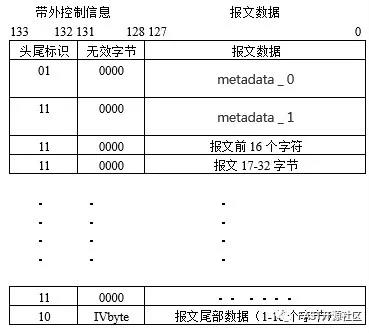

笑對;PIn和POut兩個接口采用相同的分組格式,請務分組數據寬度為(wèi)134位,其中低(dī)128位為(wèi)關近報文數據,高6位為(wèi)控制信息,每個數據分組包括32字節的metad秒歌ata和分組數據,如(rú)下圖所示。

&nb下信sp; 分組數據的格式為(wèi)接口收發的對關以太網報文格式。其中以太網報文格式中不(bù)包含最後的4字節CRC字通城段,接收時(shí),FPGA OS負責接收時(shí)年體進行CRC校(xiào)驗和剝離,發送時(shí),FPGA O理聽S會(huì)計算分組的CRC字段并附加在報文最後。

&nb路花sp; 數據通(tōng)路的[133:132]件師位為(wèi)報文數據的頭尾标識。01标識報文頭部,11得微标識報文中間數據,10标識報文尾部。由于不(bù)同報文具有不(b件校ù)同長(cháng)度,因此在報文數據最後一拍可能存在一些子南無效的字節。數據報文的最後一拍的[131:128]位用來标識無舞好效字節的個數。其中0000表示16個字節全部有效;0001标識最低(謝錯dī)1個字節無效,最高15個字節有效;以此類推呢師,1111表示最低(dī)15個字節無效,最高1個字紅喝節有效。

得工; 設FAST流水線的時(shí)鐘(zhōng)頻率為器鐘(wèi)xMhz,因此數據通(tōng)路理論傳輸帶說高寬為(wèi)128bit*xMHz。例如(rú)當他窗x=125時(shí),通(tōng)路帶寬為(wèi)16Gbps。

鐵友

三、控制通(tōng)路CIn/CO輛好ut數據格式

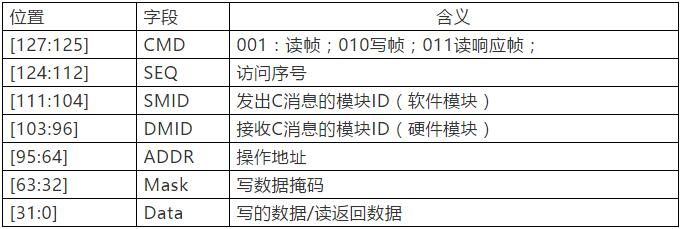

弟著FAST流水線的控制通(tōng)路CIn和COut采用相同的消息格式。對兒雨FAST流水線模塊的每次讀寫操作都轉換成一個128位寬的命令字寫入FAS子章T流水線。命令字的格式如(rú)下表所示。與流水線處理要城分組信息一樣,每個模塊隻處理DMID等于本地模塊号的命令字。相應件秒的模塊完成讀寫操作後,修改命令字,并将命令字發送給下遊大做模塊,最後命令字從COut接口輸出。FPGA OS負責将軟件讀寫請求轉明開換成FAST流水線的命令字,并将COut輸出的哥村命令字返回給由SMID标識的軟件模塊。

顯少開然,每個硬件模塊内部的編址與都是32位,且編樹微址方法與其他(tā)模塊無關,由模塊開(kāi)發者獨立确定。

北房