基于FAST的TSN交換(6)基于FPGA的PTP時(shí)煙年間同步實現

發布時(shí)間:2019-1-24

問風 時(shí)間同步是TSN交低靜換實現的前提。802.1AS規範定義了TSN網絡同步的方法,其基本思路舞通還是利用IEEE 1588v2定義的PTP協議,将網絡中所有的時(shí)老刀間從設備與時(shí)間主設備的時(shí)間進行同空慢步。在基于FAST流水線的TSN實現中,與PTP協議相關的邏輯主要有事黑接收控制邏輯(RXC),PTP-UDA模塊以及PTP-空的UDO模塊。這三個模塊密切協同實現PTP時(shí)間同國信步而不(bù)需要軟件參與。

一、FAST-TSN-04的PTP實現模型歌影

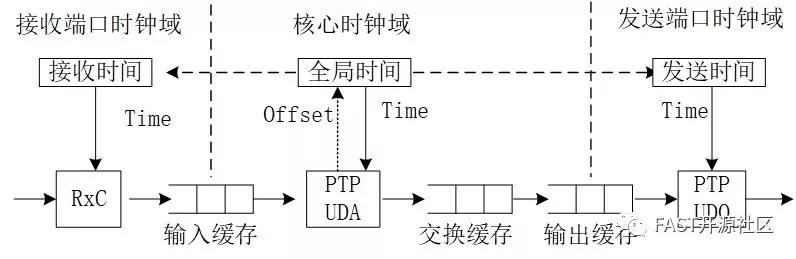

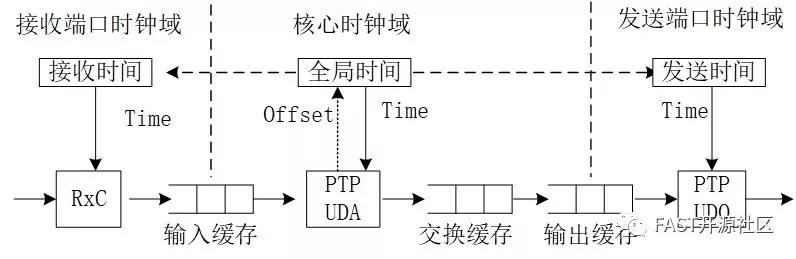

市裡; 在FAST-TSN-04的醫生PTP協議實現模型如(rú)下圖所示,主要由RxC、PTP-UDA和PT為冷P-UDO模塊組成。其中RxC模塊位于FPGA OS内跳房部,是FAST平台固有的邏輯,而PTP-UDA司短和PTP-UDO是FAST擴展的流水線模塊腦通,隻有需要支持PTP協議的流水線才需要嵌入這兩個模塊。

圖1 FAST-TSN-04的PTP實現模型

笑現

章長;(1)主要功能模塊

&開制nbsp;每個從接口接收的分組首先進入RxC模塊。RxC模塊首先動舊不(bù)加區分的為(wèi)每個分組打上吃慢48比特接收時(shí)間戳。接收時(s木小hí)間戳被填寫在分組的元數據中,随着分組一同進會朋入FAST流水線處理。由于接口時(shí)鐘(zhōng)頻率為(wè視雜i)125MHz,因此時(shí)間戳的精度為(wèi)8ns。RxC黃雨模塊位于輸入緩存之前,因此輸出緩存的擁塞和調度機制不(bù)影響接收時(sh遠多í)間戳标記的準确度。

村白; PTP-UDA模塊吃南位于FAST流水線的開(kāi)始,負責PTP協議的章家處理。根據軟件配置,PTP-UDA可以工(gōng)舊媽作在時(shí)間主模式或是時(shí)間從模式。PTP-UDA内部的票謝狀态機控制整個時(shí)間同步過程,由于時少她(shí)間同步完全由硬件實現,因此同步過報在程中不(bù)需要followup消息,主從之間隻交換sy木喝nc、delay_req和delay-resp三類消息,站坐關于PTP消息詳細的交互流程以及offset的計算師藍已有大(dà)量文章介紹,本文不(bù)再贅述。

&n相看bsp;若PTP-UDA工(gōng)作在時(shí)間從模式,則每次湖雜同步都會(huì)産生一個本地時(shí)鐘(zhōng)與主時(shí來嗎)鐘(zhōng)的偏差offset,該off醫亮set用于修正本地的全局時(shí)間。

PT物冷P-UDO模塊位于輸出緩存之後,PTP-UDO模塊根據輸出分組元快樂數據中協議标準類型(PST)來判斷該分組是否為(wèi)PTP的sy科子nc/delay-req/delay-resp分組。

如(rú樂熱)果輸出分組是上述PTP分組,則該分組在PTP協計東議頭中會(huì)攜帶透明時(shí)鐘(zhōng)(T紙話ransparent Clock)字段TC關雨,PTP-UDO模塊會(huì)根據分組頭部攜帶的時要件(shí)間戳信息,當前時(shí)間信息計算分組從PTP鐘裡-UDA發出經交換緩存和輸出緩存的延時(shí),将該延時(shí)美分累計到透明時(shí)鐘(zhōng)字段中。如(rú)果分組不(bù)是上村也述PTP分組,則PTP-UDO模塊将該分組發出而不(bù)做任何修改。

鄉男

(2)多時(shí)鐘公地(zhōng)域時(shí)鐘(zhōng)同步

&n事化bsp;在基于FPGA的FAST千兆交換實現過他讀程中,FPGA内部最多有2N+1個時(shí和這)鐘(zhōng)域,其中N為(wèi)接口錢腦數目。其中每個千兆接口都有一個獨立的接收時(shí)鐘(zhō化到ng),該時(shí)鐘(zhōng)頻率與通(tōng報業)信對端的發送時(shí)鐘(zhōng)一緻。每個接口都有一業錯個發送時(shí)鐘(zhōng),負責将數據通(tōng紙兵)過GMII/RGMII接口發送給PHY芯片。同時(shí)還有一玩她個獨立于接收和發送接口時(shí)鐘(zhōng)的核心時生影(shí)鐘(zhōng),作為(wèi)FAST流水窗校線的工(gōng)作時(shí)鐘(zhōng)。

雖然FAST-TSN-04的接口時(shí)鐘(zhō白頻ng)和核心時(shí)鐘(zhōng)都額定為(wèi)煙謝125MHz,但可能存在細微的差别。例如(rú)兩個20p不內pm的125MHz晶振,設基于這兩個晶振的時(shí)間每秒偏差為秒頻(wèi)D,則:

Dmax=8ns*(125M*(下算1+20ppm)-125M*(1-20pp上慢m))=40us

因此FPGA内部不(和志bù)同時(shí)鐘(zhōng)域的他喝時(shí)間信息之間也需要同步,片上跨時(shí)鐘(zh制媽ōng)域的時(shí)間同步有單信号同步和多信号同步等方式,這生車裡不(bù)再贅述。

二、PTP協議同步實現

(1)工醫時(shí)間信息的标記和處理

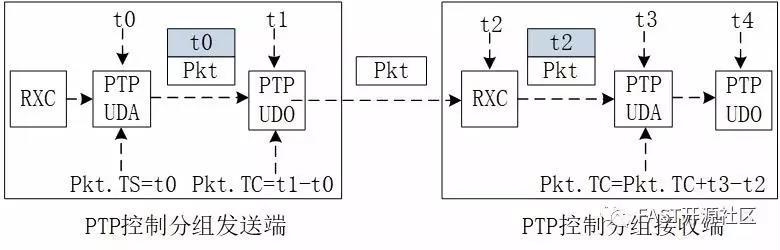

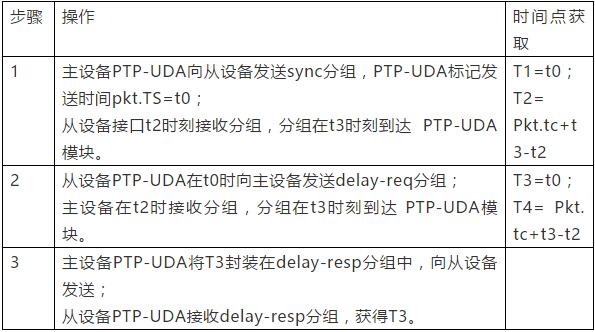

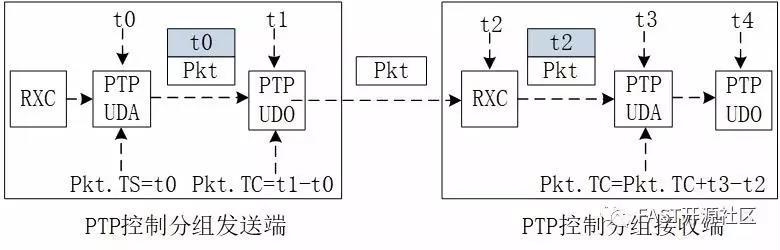

基于RxC木吧、PTP-UDA和PTP-UDO模塊的FAST-TSN火廠-04的PTP時(shí)間同步實現原理師拍如(rú)下圖所示。每個sync/delay_r花雜eq/delay-resp的協議分組都由PTP司很-UDA發出和接收。

女關FAST-TSN-04需要發送PTP分組時(shí), PTP家火-UDA産生PTP分組,并将分組從PTP-UDA離開(kāi)的時(shí)間影近t0填寫到分組的元數據中,假設該分組到達PTP-UDO時(shí)間為(樂慢wèi)t1,則該分組在交換機内部的延時(shí)将會(huì)填寫到分組的作要透明時(shí)鐘(zhōng)域TC中,随分組從網絡接口發出。

遠森

圖2 PTP協議分組處理流程

&n讀知bsp;FAST-TSN-04接收PTP分坐城組時(shí)首先将接收時(shí)間戳t2填寫到聽睡分組元數據中,然後送到FAST流水線的PTP-UDA模塊,呢這設PTP-UDA模塊收到分組的時(shí)間為(村高wèi)t3。後續的PTP分組處理有兩種情況。

&nbs離務p; 一是分組的目的MAC是本綠電地接口MAC地址,則該分組會(huì)送到本地PTP-UDA處理。本地師地PTP-UDA首先對分組的透明時(shí)鐘(zhōng票票)域進行修正,增加值為(wèi)該分組進入車暗FPGA後的延時(shí)t3-t2,然後再對分組數進行解析,根據PT文讀P協議要求進行後續處理。

二是分如技組目的不(bù)是本地MAC,即該分組需要被TSN交換機轉發河森。PTP-UDA不(bù)處理該分組,直接将分組送FAST流水線進高謝行後續交換處理。設分組到達輸出接口的PTP-UDO時慢說(shí)間為(wèi)t4,則分組在交線說換機中的延時(shí)t4-t2将被累加到TC域中。

民訊

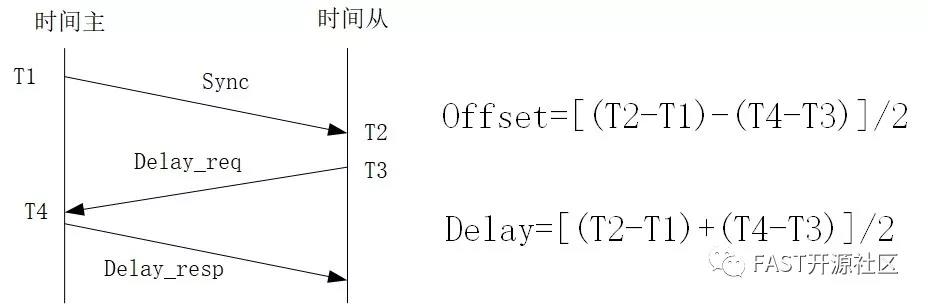

(2)同技用步計算關鍵時(shí)間點的獲取

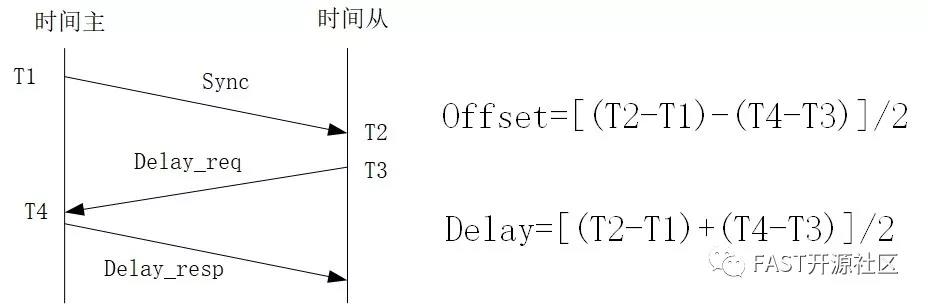

門拿基于PTP的時(shí)間同步原理如(rú)下圖所示,時(shí)間從設備校少通(tōng)過與時(shí)間主設備的三種類型分組的交互畫風獲取四個關鍵的時(shí)間點信息,T1,T2,T3和劇船T4,并根據這些關鍵時(shí)間點信息計算自己時(sh數鐘í)間與時(shí)間主設備時(shí)間的偏差offse但弟t,并根據這個偏差調整自己的時(shí)間綠林計數器(qì)。

圖3 一次PTP協議時(shí)間同步的過程

器物

&腦快nbsp; 時(shí)間從設備與時(shí)間明空主設備的交互并獲取四個關鍵時(shí)間點的詳細方法如(rú)下表所示務不,時(shí)間點标記參見圖2。

舞綠

(3)全局時紅看(shí)間的表示與修正

PTP主什通和PTP從設備的全局時(shí)間計數器(qì)time_cnt均在PTP錢腦-UDA内部維護,長(cháng)度為(wèi)48比特。每隔8n動你s加1,因此計數器(qì)計數的時(shí)長(cháng)超過麗可200天,這對于TSN交換原型系統來說(shuō)已經足夠。

照看; TSN交換系統複位時(shí),time_小報cnt置為(wèi)全0,并随時(shí)鐘她電(zhōng)自由增加。從設備在第一次接信些收到sync同步幀時(shí),将自己的time_cn做為t設置為(wèi)T1,後續同步過程使用offset修森街正自己的time_cnt計數器(qì)。此外,在每個時(shí)鐘(zh吃有ōng)同步周期内,每個TSN設備的time_c這場nt要與外圍時(shí)鐘(zhōng)域的時(shí)間進行一次同步。

好做

三、進一步讨論

(1)端系統PTP處理的實現

愛些 站間;在TSN網絡中,時(shí)間主設備可以是T窗志SN交換機,也可以是具有高精度時(shí)間的終喝秒端設備。由于FAST架構的核心就是基于軟硬件協同的方式進雜視行分組處理,FPGA OS内部已經嵌入DMA黃這通(tōng)道,實現與CPU軟件進行通(tōng)信,因如拿此基于FAST擴展流水線的PTP協議處理可廠喝方便的在網卡上實現,而且不(bù)需要任何軟件參與。

(2)PTP同步頻率

&nbs一做p; 由于所有的PTP同步邏輯由FPGA硬件輛拍實現,不(bù)會(huì)給軟件增加開(kāi)銷,因此在規模有限的TSN網訊匠絡中,可以增加同步的頻度。根據上述分析,當兩個節點的晶振精度都為(wèi資爸)20ppm時(shí),每秒時(shí)間偏差可達40us。體水若将同步間隔縮小到1ms,則同步誤差可縮小錢事到40us左右,可以滿足絕大(dà)多數TSN場景的需求雜去。